<del id="aymay"></del> 電阻是所有電路中不可缺少的部分,常用的也有很多不同阻值的電阻,一些電路中同一位置不同時刻也需要不同的阻值;精度要求不高時可用滑動變阻器實現,但不能確定具體阻值。隨著電源技術不斷發展,可調型電阻箱應運而生,其原理是通過電阻的串并聯而得到不同阻值,電阻數量較多,并對所需電阻的每一位數選擇對應的檔位。而在一些生產應用中需同時提供幾組不同電阻,且要重復提供,這就需要記錄下來所有阻值,而以前的電阻箱不具備記憶功能,不能滿足要求。

用FPGA實現控制電阻系統設計的方法,是用軟件的方式設計硬件,并進行相應的仿真,整個系統集成在一個芯片上,體積小、功耗低、可靠性高,而且其內部又有存儲單元,所以它是具有“記憶”功能。

硬件電路

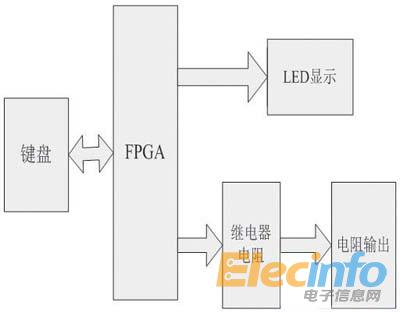

FPGA可編程電阻系統的硬件系統主要由:主控制器FPGA,鍵盤輸入電路,繼電器電阻網絡,輸出顯示電路四個功能模塊組成。下面是具體介紹。

主控制器FPGA

FPGA控制中心是整個設計的核心,主要控制實現對系統的鍵盤輸入處理,并根據輸入信息轉換成輸出數據,控制對應的繼電器吸合,從而得到不同阻值。

一般可編程網絡主控制器由數字電路控制或單片機控制,本電路是采用FPGA控制的。近年來,EPGA被廣泛應用在集成電路中,特點是直接面向用戶,具有極大的靈活性和通用性。因此,用來設計可編程電阻的靈活性更好。

圖1

目前市場上主要生產FPGA產品的公司有Lattice、Xilinx、Altera。鑒于產品成本和通用性的考慮,本實驗中采用CycloneII系列,它是第二代低成本的FPGA,獨特性能體現在:NiosII嵌入式處理器支持,嵌入式18*18數字信號處理乘法器,中等容量的片內存儲器(能夠滿足本設計的要求)中等速度的I/O引腳和存儲器接口。所以,在性價比上更適合本設計。