<del id="aymay"></del> 在現代電子產品的故障維修或檢測中,需要的是穩定的頻率和幅度來滿足自動調節的正弦信號源,并且要求轉換速度快,具有調頻、調幅、調相的功能。本文原理與實際相結合,提出一種基于單片機和FPGA的直接頻率數字合成器的設計方案,產生兩路頻率和相位調節的正弦波信號,并達到預期效果。

1.系統方案設計

1.1 系統的性能分析

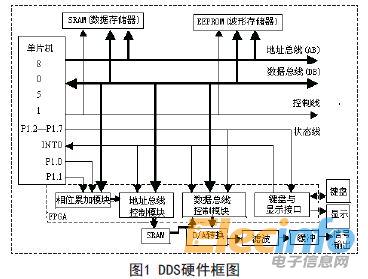

系統主要由單片機最小系統、存儲器電路、FPGA模塊、鍵盤與顯示接口電路、D/A轉換電路、低通濾波電路組成,其硬件框圖如圖1所示。通過鍵盤輸入頻率控制字、相位控制字和幅值控制字,單片機最小系統控制FPGA模塊產生用戶需要的正弦波信號,再經過DA轉換,最后通過低通濾波器生成平滑的正弦波信號。

系統的性能要求:頻率范圍20Hz~20KHZ,步進20Hz;差0o~359o,步進1o;兩路輸出正弦波信號,峰峰值分別在0.3V~5V變化;數字顯示頻率、相位差。

1.2 系統實現的原理

1.1.1 DDS的基本原理

直接數字頻率合成器(DDFS)的基本原理:

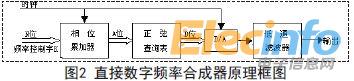

DDS是利用采樣定理,根據相位間隔對正弦信號進行取樣、量化、編碼,然后儲存在EPROM中構成一個正弦查詢表,通過查表法產生波形。

它是由參考時鐘、相位累加器、正弦查詢表和D/A轉換器組成,如圖2所示。

相位累加器由N位加法器與N位累加寄存器級聯構成,其原理框圖如圖3所示。每來一個時鐘脈沖Fc,N位加法器將頻率控制數據K與累加寄存器輸出的累加相位數據相加,把相加后的結果Y送至累加寄存器的輸入端。累加寄存器一方面將在上一時鐘周期作用后所產生的新的相位數據反饋到加法器的輸入端,以使加法器在下一時鐘的作用下繼續與頻率控制數據K相加;另一方面以相加后的結果形成正弦查詢表的地址,取出表中與該相位對應的單元中的幅度量化正弦函數值,作為取樣地址值送入幅度/相位轉換電路。這樣就可把存儲在波形存儲器內的波形抽樣值(二進制編碼)經查找表查出,完成相位到幅值轉換。波形存儲器的輸出送到D/A轉換器,D/A轉換器將數字量形式的波形幅值轉換成所要求合成頻率的模擬量形式信號。

相位累加器的最大計數長度與正弦查詢表中所存儲的相位分隔點數相同,在取樣頻率(由參考時鐘頻率決定)不變的情況下,由于相位累加器的相位增量不同,將導致一周期內的取樣點數不同,輸出信號的頻率也相應變化。

如果設定累加器的初始相位,則可以對輸出信號進行相位控制。由采樣原理可知,如果使用兩個相同的頻率合成器,并使其參考時鐘相同,同時設定相同的頻率控制字、不同的初始相位,那么在原理上就可以實現輸出兩路具有一定相位差的同頻信號。